EEL814 – Microeletrônica I – 2º. Semestre/2019 – DEL/UFRJ Prof. Antonio Petraglia

# **Direct-Form SC Filters**

## **Direct-Form FIR SC Filter Realization**

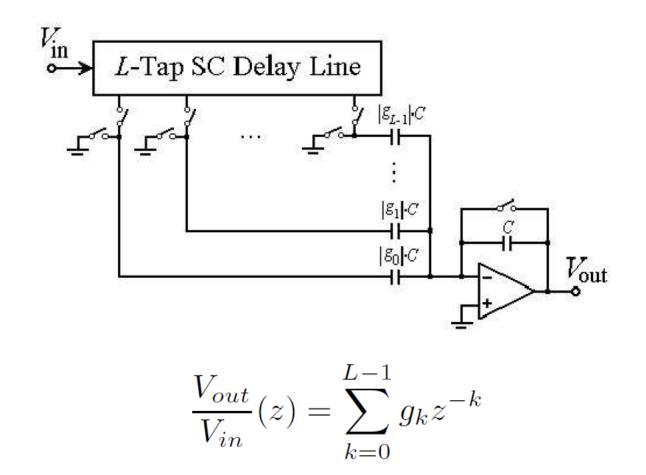

(L-1)th-order FIR SC filter:

# **Direct-Form FIR SC Filter Realization**

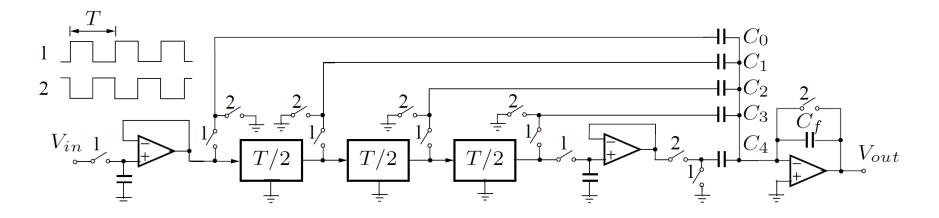

Ex.: 4<sup>th</sup>-order SC FIR filter

$\frac{V_{out}}{V_{in}}(z) = -\frac{C_0}{C_f} - \frac{C_1}{C_f} z^{-1} - \frac{C_2}{C_f} z^{-2} - \frac{C_3}{C_f} z^{-3} + \frac{C_4}{C_f} z^{-4}$

## **Direct-Form FIR SC Filter Realization**

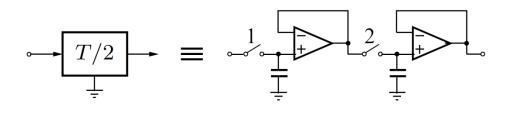

Reduction of the number of amplifiers by a multiplexing technique

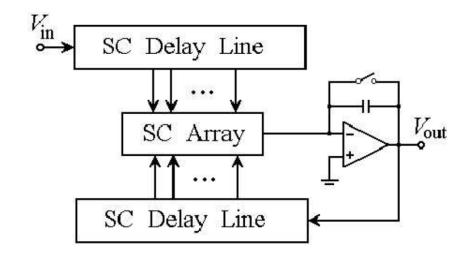

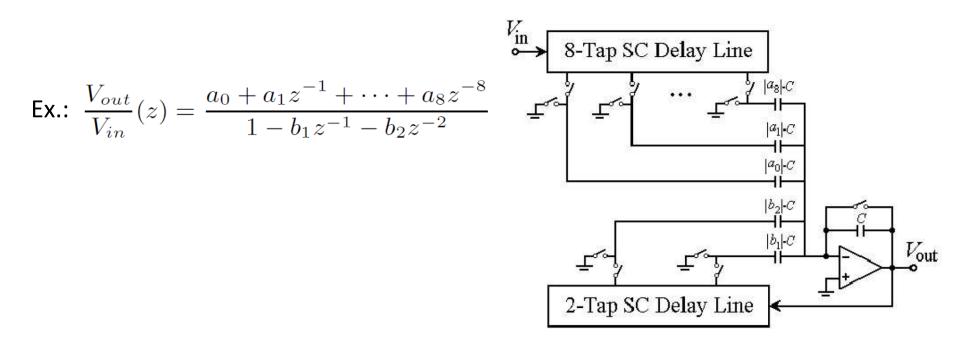

### **Direct-Form IIR SC Filter Realization**

#### Direct Form I

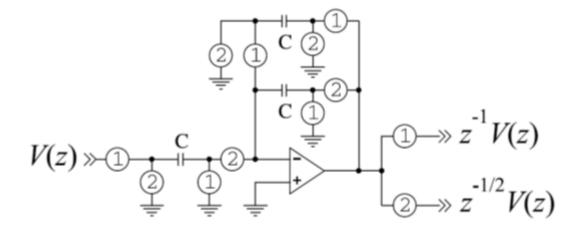

2 SC delay lines sharing the same SC array

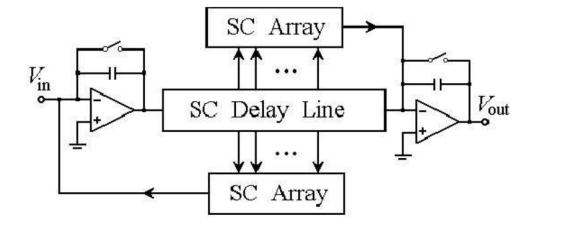

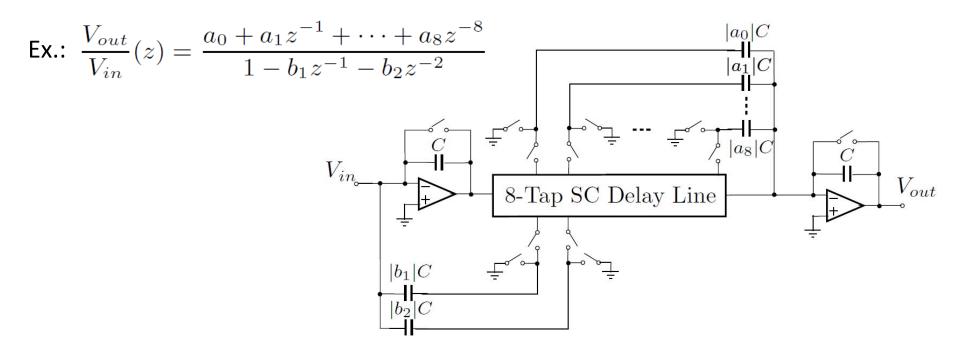

### **Direct-Form IIR SC Filter Realization**

#### Direct Form II

2 SC arrays sharing the same SC delay line

# **Capacitors in CMOS Technology**

### **Aplications in which capacitance matching is critical issue:**

- Converters: A/D, D/A, DC/DC

- Switched-capacitor filters

### **Capacitance mismatch sources in CMOS IC's:**

- Process gradient ( $t_{ox}$ )

- Random errors

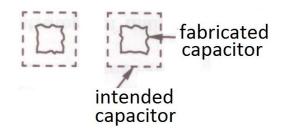

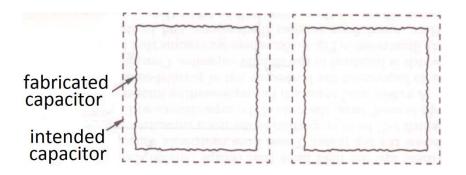

# **Capacitors in CMOS Technology**

#### **Capacitors too small:**

- The actual capacitance ratio can be significantly different from unity.

#### Larger capacitors:

- Better ratio accuracy;

- However, if the plates are too large: (i) chip area may be excessive;

(ii) opposite regions of the two capacitors may be affected differently by the fabrication process (e.g., slightly difference in oxide thickness);

# **Capacitors in CMOS Technology**

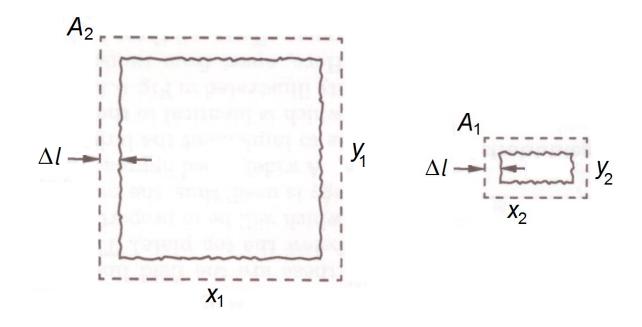

#### Sistematic errors:

- The relative area error of two capacitors will be the same if the nominal perimeter/area ratio is the same;

- Therefore the capacitance ratio will not be affected.

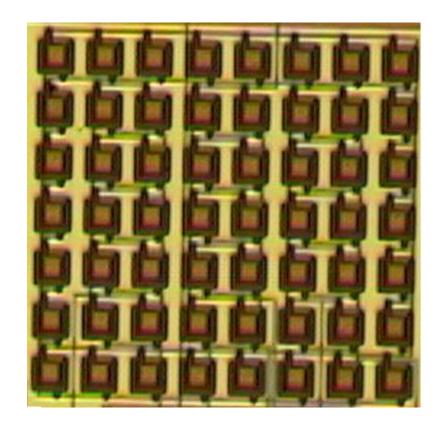

# **Capacitor Layout**

**Techniques to improve capacitance matching:**

- Parallel connection of identical unit capacitors to implement each capacitance;

- Arrangement of unit capacitors in common centroid symmetry;

- Careful routing inside capacitor matrices.

Unit capacitor arrangement: C = 100 fF, 5μmx5μm

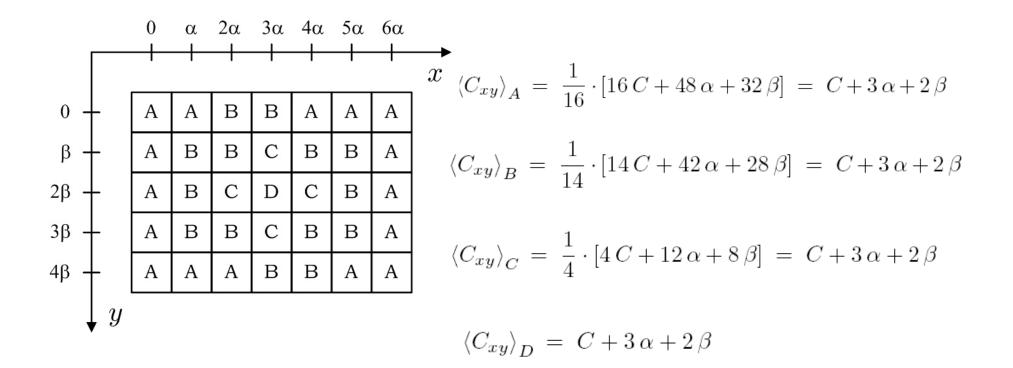

### **Capacitor Layout**

Common centroid geometry - evaluation of the mean unit capacitance of each capacitor, assuming the linear model for  $t_{ox}$ :

#### **Difficulties:**

- Common centroid arrangement is not a simple task when the number of capacitance ratios is large;

- Common centroid geometry is not always possible;

- When it is possible, there are several alternatives;

#### **Solutions:**

- Develop an algorithm to search for the best arrangement among different possibilities;

- Find the optimal arrangement that doesn't have symmetry when common centroid is not possible.

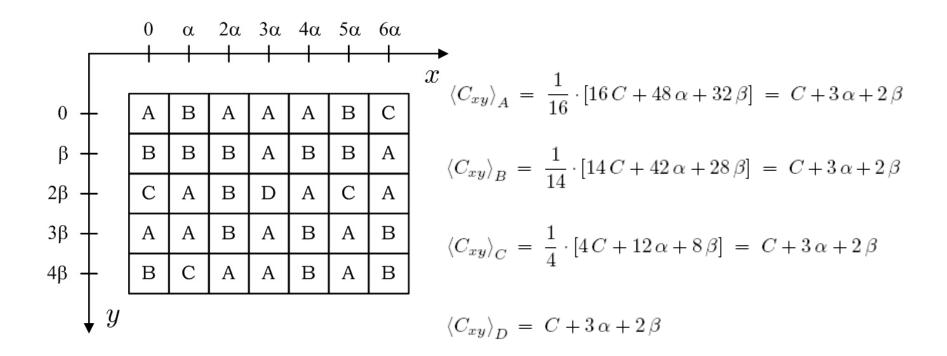

### **Capacitor Layout**

Example without common centroid, but insensitive to process gradient:

C.F.T. Soares, A.C.M. Filho and A. Petraglia, IEEE Trans. Evolutionary Computation, Jun. 2010.

## **Capacitance Mismatch Effects**

Mathematical model commonly used in computer aided analysis of SC filters:

$$\hat{\gamma_k} = \gamma_k + \epsilon_{\gamma_k}$$

were  $\epsilon_{\gamma_k} = \gamma_k \epsilon_k$

$\gamma_k$  : capacitance ratios

$\epsilon_k$ : uncorrelated zero-mean Gaussian random variables

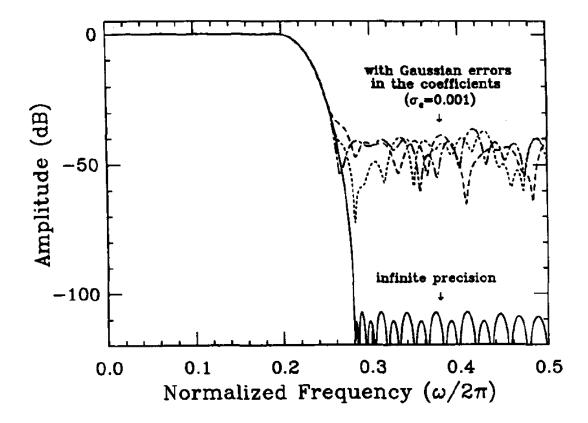

### **Capacitance Mismatch Effects**

Ex.: Frequency responses of 3 FIR filters having L = 50 and  $\sigma_e$  = 0.001

EEL814 – Microeletrônica I – 2°. Semestre/2019 – DEL/UFRJ Prof. Antonio Petraglia