# **Analog Decimation Filters**

A. Petraglia

Universidade Federal do Rio de Janeiro

DEL, COPPE

#### **Decimation and Interpolation Filters**

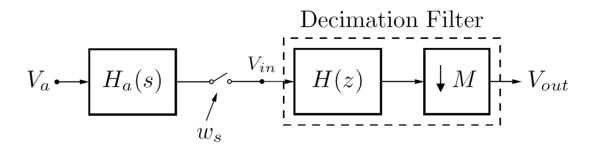

#### **Decimation Filter**

$$V_{in}$$

$H(z)$   $\downarrow$   $M$   $\downarrow$   $V_{out}$  • The cascade of a lowpass filter and a down-sampler is called a decimation filter:

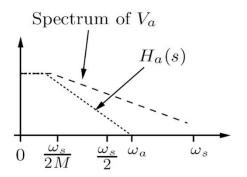

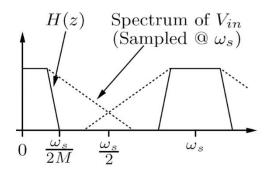

#### Ideal Frequency Response

$$H(e^{j\omega}) = \begin{cases} 1, & |\omega| \le \omega_s/2M \\ 0, & \omega_s/2M < |\omega| \le \omega_s/2 \end{cases}$$

- decimation filter;

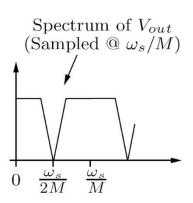

- Filter H(z) attenuates input frequency components greater than  $\omega_{\rm s}/2M$ ;

- The sampling rate can then be reduced by the factor *M*.

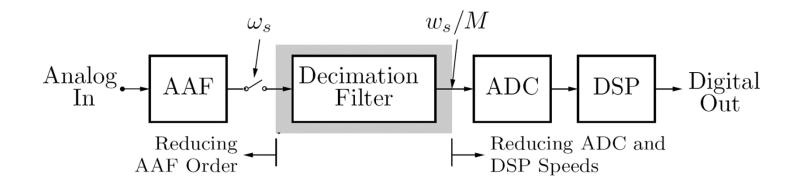

### **Sampling of Analog Signals**

### **Sampling of Analog Signals**

- Output of the anti-aliasing filter (AAF) is oversampled by factor *M*:

- → transition band of AAF can be increased;

- Accurate bandlimiting provided by SC filter H(z) allows sampling rate reduction:

- $\rightarrow$  reduction of ADC and DSP power consumption.

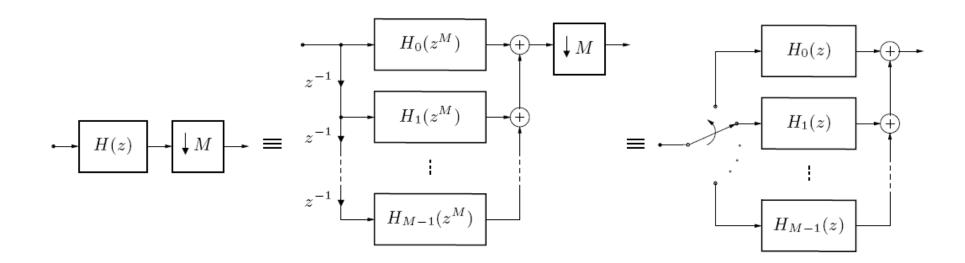

#### FIR Decimation Filters

$$H(z) = h(0) + h(1)z^{-1} + h(2)z^{-2} + \dots + h(7)z^{-7}$$

$$= h(0) + h(3)z^{-3} + h(6)z^{-6} + z^{-1} \underbrace{\left(h(1) + h(4)z^{-3} + h(7)z^{-6}\right)}_{H_1(z^3)} + z^{-2} \underbrace{\left(h(2) + h(5)z^{-3}\right)}_{H_2(z^3)}$$

$$= H_0(z^3) + z^{-1}H_1(z^3) + z^{-2}H_2(z^3)$$

#### In the general case:

$$H(z) = \sum_{n=0}^{N-1} h(n)z^{-n} = \sum_{k=0}^{M-1} z^{-k} H_k(z^M)$$

#### **FIR Decimation Filters**

$$H(z) = \sum_{n=0}^{N-1} h(n)z^{-n} = \sum_{k=0}^{M-1} z^{-k} H_k(z^M)$$

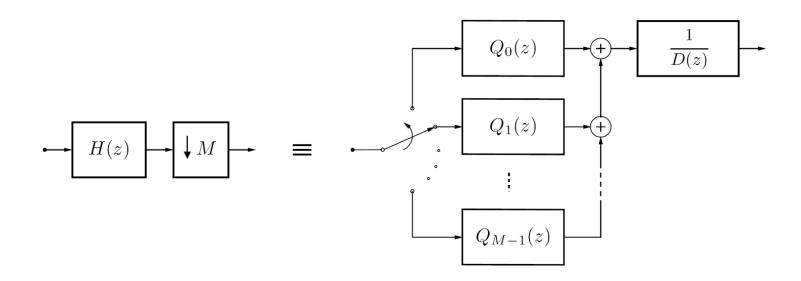

#### **IIR Decimation Filters**

$$H(z) = \frac{A(z)}{B(z)} = \frac{A(z)P(z)}{B(z)P(z)} = \frac{Q(z)}{D(z^M)} = \frac{\sum_{k=0}^{M-1} z^{-k} Q_k(z^M)}{D(z^M)}$$

$$H(z) = \sum_{k=0}^{M-1} z^{-k} H_k(z^M)$$

$H_k(z) = \frac{Q_k(z)}{D(z)}$

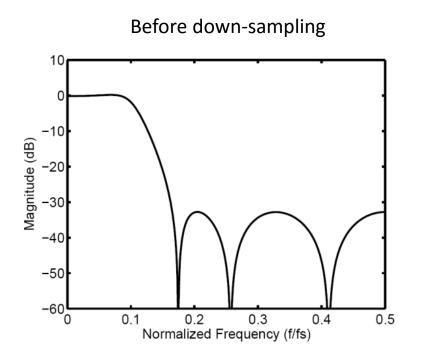

#### Design Example

- passband edge frequency = 2.5 MHz

- stopband edge frequency = 4.5 MHz

- passband ripple < 0.4 dB

- stopband attenuation > 25 dB

- Decimation factor M = 3

- Input sampling rate = 30 MHz

The filter transfer function has been designed with 6 zeros and 2 poles

- low sensitivity to coefficient errors -> small capacitance spread

- small circuit complexity -> low power consumption

The filter transfer function has been designed with 6 zeros and 2 poles:

$$a_{0} = 0.0405$$

$$a_{1} = 0.0353$$

$$H(z) = \frac{A(z)}{B(z)} = \frac{A(z)P(z)}{B(z)P(z)} = \frac{Q(z)}{D(z^{M})} = \frac{\sum_{k=0}^{M-1} z^{-k}Q_{k}(z^{M})}{D(z^{M})}$$

$$a_{2} = 0.0615$$

$$a_{3} = 0.0651$$

$$a_{4} = 0.0615$$

$$a_{5} = 0.0353$$

$$a_{6} = 0.0405$$

$$D(z) = 1 + 0.3369z^{-1} + 0.2915z^{-2}$$

$$b_{0} = 1.0000$$

$$b_{1} = -1.3166$$

$$b_{2} = 0.6631$$

$$H(z) = \frac{A(z)P(z)}{B(z)P(z)} = \frac{Q(z)}{D(z^{M})} = \frac{\sum_{k=0}^{M-1} z^{-k}Q_{k}(z^{M})}{D(z^{M})}$$

$$D(z^{M})$$

$$D(z^{M}) = \frac{1}{D(z^{M})}$$

$$D(z^{M}) = \frac{1}{D(z^{M})}$$

$$D(z^{M}) = \frac{1}{D(z^{M})}$$

$$D(z^{M}) = \frac{1}{D(z^{M})}$$

#### Coefficients of the polyphase components:

| The second second |        |                   |                |

|-------------------|--------|-------------------|----------------|

| H(z)              |        | $Q_k(z)$          | D(z)           |

| $a_0 =$           | 0.0405 | $q_{00} = 0.0405$ | $d_0 = 1.0000$ |

| $a_1 =$           | 0.0353 | $q_{01} = 0.2192$ | $d_1 = 0.3369$ |

| $a_2 =$           | 0.0615 | $q_{02} = 0.2366$ | $d_2 = 0.2915$ |

| $a_3 =$           | 0.0651 | $q_{03} = 0.0509$ |                |

| $a_4 =$           | 0.0615 | $q_{10} = 0.0886$ |                |

| $a_5 =$           | 0.0353 | $q_{11} = 0.2616$ |                |

| $a_6 =$           | 0.0405 | $q_{12} = 0.1734$ |                |

| $b_0 =$           | 1.0000 | $q_{13} = 0.0178$ |                |

| $b_1 = -$         | 1.3166 | $q_{20} = 0.1513$ |                |

| $b_2 =$           | 0.6631 | $q_{21} = 0.2550$ |                |

|                   |        | $q_{22} = 0.1012$ |                |

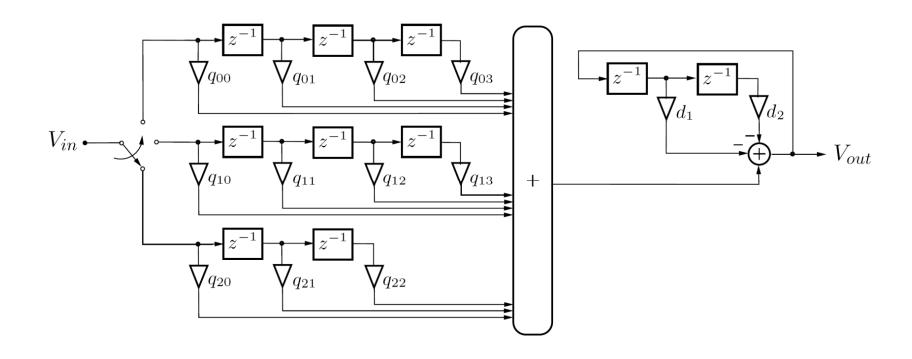

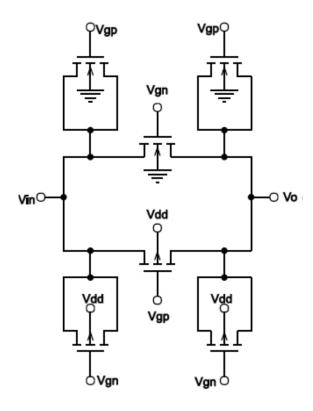

#### Block diagram of the decimation filter

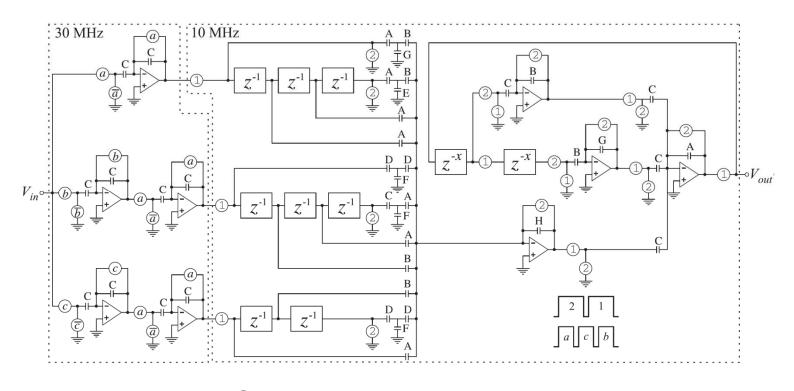

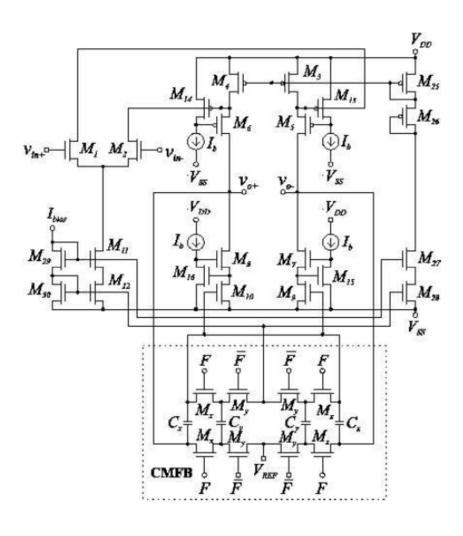

#### Schematic diagram of the decimation filter

| A = 0.2  pF | E = 0.7 pF |

|-------------|------------|

| B = 0.3 pF  | F = 0.8 pF |

| C = 0.1 pF  | G = 0.9 pF |

| D = 0.4 pF  | H = 1.2 pF |

Capacitances are implemented by parallel associations of identical 0.1 pF units

| E = 0.7 pF |

|------------|

| F = 0.8 pF |

| G = 0.9 pF |

| H = 1.2 pF |

|            |

Switches are implemented with dummy transistors to reduce charge injection

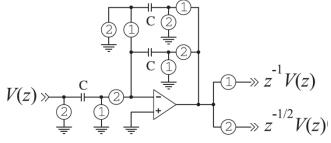

#### Operational transconductance amplifiers

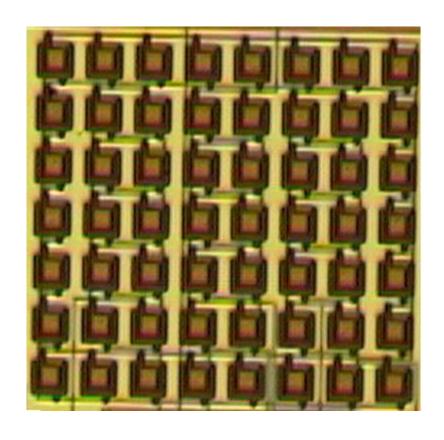

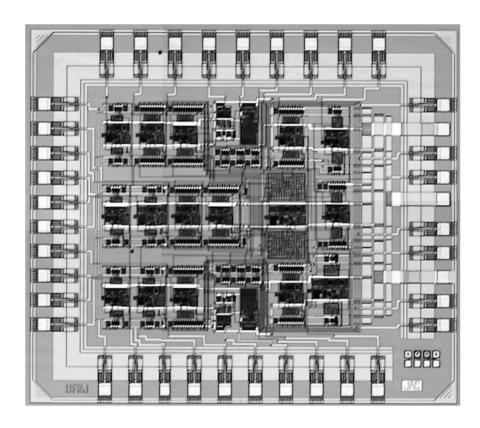

Chip photograph – Die area =  $1.86 \times 1.50 \text{ mm}^2$

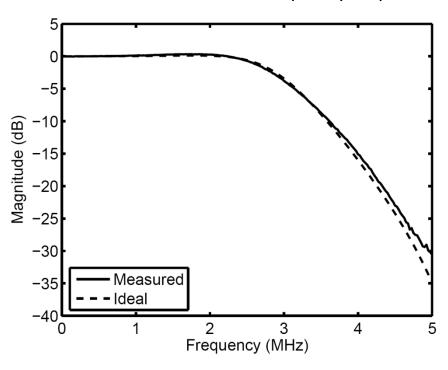

#### Measured and ideal frequency responses

| Voltage Supply            | 5V                 |

|---------------------------|--------------------|

| Input Sampling Frequency  | $30~\mathrm{MHz}$  |

| Output Sampling Frequency | $10~\mathrm{MHz}$  |

| Dynamic Range (1% THD)    | 58  dB             |

| Dye Area                  | $2.8 \text{ mm}^2$ |

| Power Consumption         | $67.2~\mathrm{mW}$ |

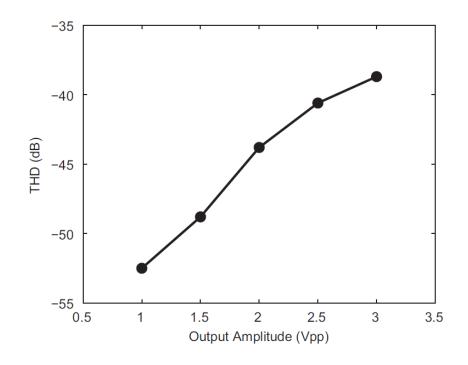

Measured harmonic distortion